반도체 메모리의 저장용량을 획기적으로 늘릴 수 있는 신(新)개념 회로 기술을 한국과 미국 과학자들이 공동 개발했다.

이 기술을 활용하면 휴대전화에 노래나 게임을 지금의 수십 배까지 내려받을 수 있고 컴퓨터 마이크로프로세서와 메모리 기능을 동시에 갖춘 다기능 칩도 만들 수 있다.

국가나노종합팹센터와 한국계 미국 벤처기업 ‘비상’, 미국 스탠퍼드대 나노팹 연구원들로 구성된 연구팀은 반도체 회로를 여러 층으로 쌓아 집적도를 높인 3차원(3D) 집적회로(IC) 기술을 개발해 11일 서울 강남구 삼성동 그랜드인터컨티넨탈호텔에서 시연회를 열었다.

평면 실리콘 기판에 회로를 그리는 방식의 기존 IC는 용량을 늘리는 데 한계가 있어 과학자들은 3D 반도체를 만들기 위해 노력해 왔지만 그동안 채산성 있는 기술을 개발하지 못했다.

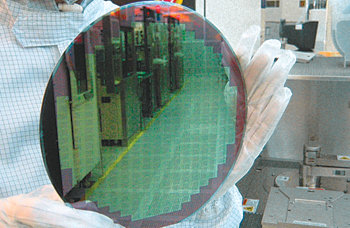

그러나 한미 연구팀은 1년간의 연구 끝에 일반 반도체 공정에서 사용되는 지름 8인치 웨이퍼에 2층으로 집적회로를 쌓는 데 성공했다. 국가나노종합팹센터 측은 “3D IC 기술로 반도체 회로를 여러 층 쌓으면 저장용량을 수십 배로 늘릴 수 있다”고 밝혔다.

3D IC 기술이 상용화되면 동일한 웨이퍼에서 더 많은 반도체 칩을 만들 수 있어 생산비용이 크게 줄어들고 한 개의 칩이 여러 기능을 수행하는 다기능 반도체 칩의 개발도 가능해진다. 비상은 내년 중반까지 이 기술을 상용화할 계획이다.

박근태 동아사이언스 기자 kunta@donga.com

-

- 좋아요

- 0개

-

- 슬퍼요

- 0개

-

- 화나요

- 0개