제10회 SK하이닉스 학술대회 개최

반도체 전 분야 논문 연평균 680편 접수

전략 특허로 이어져 기술 개발의 토양

D램·낸드 최신 기술 극복방안도 논의

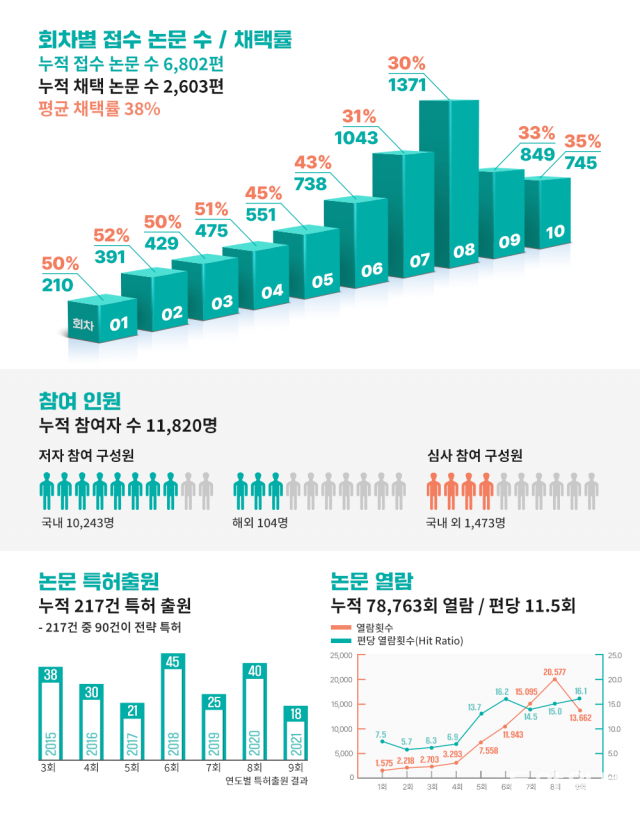

논문 누적 6802편 접수, 2603편 채택. 217건 특허 출원, 90건 전략 특허. 구성원 1만1820명 참여.

올해 10회를 맞은 SK하이닉스 학술대회의 성과다. SK하이닉스는 구성원들의 기술개발을 장려하고 아이디어를 공유하기 위해 2013년부터 매년 학술대회를 열고 있다. 소자·공정·설계·패키징 등 반도체 전 분야에 걸친 주제의 논문이 연평균 680여 편 접수됐다. ‘반도체 올림픽’이라고 불리는 국제고체회로학회(ISSCC)의 연간 접수 논문 평균인 600편에 버금가는 수준이다.

4일 SK하이닉스에 따르면 지난달 24~28일 5일간 열린 이번 학술대회에서는 총 745편의 논문이 접수됐고 260편이 입선했다. 채택률 35%다.

학술대회에서 발표된 논문의 누적 열람수는 7만8763회다. 평균 11.5회다. SK하이닉스 측은 “논문이 발표 직후 사장되는 게 아니라 연구를 위해 활발히 사용되고 있다는 걸 뜻한다”며 “특히 내부 학술대회의 논문은 외부 학회 논문에서는 알 수 없는 SK하이닉스 고유 데이터와 연구 성과를 담고 있어 실용적인 도움이 크다”고 전했다.

이에 맞춰 지난 10년을 이끈 기술을 꼽는 투표를 진행하고 발표하는 자리도 마련했다. D램 분야에서는 좁은 면적에 소자를 쌓아 셀의 집적도를 높이는 ‘6F2’, 10나노(nm·1nm는 10억분의 1m) 기술 진입을 가능하게 한 ‘Buried Gate’ 등이 뽑혔고 낸드에서는 웨이퍼에 칩을 더 많이 생산할 수 있게 한 ‘PUC’ 등이 선정됐다.

정수옥 미래기술연구원 담당은 10나노급을 넘어선 D램이 맞닥뜨린 기술적 한계와 다양한 시도에 대해 이야기했다. 오상현 미래기술연구원 담당은 낸드를 주제로 500층 이상의 적층 문제를 극복하기 위한 기술에 대해 설명했다. 현재 D램은 기업들이 3나노 양산에 나서기 시작했고 낸드는 200단급을 앞다퉈 선보이고 있다. D램은 공정이 더 미세화 할수록, 낸드는 층이 더 많이 쌓일수록 성능이 올라가고 전력 효율도 높아진다.

곽노정 SK하이닉스 대표는 “벌써 10년째를 맞이한 학술대회가 처음 열었을 때에 비해 엄청난 발전을 이뤘고 예나 지금이나 참가하는 구성원들의 열정도 변하지 않았다”며 “우리가 논문을 써야 하는 이유는 올해의 슬로건 잘 담겨 있다. 일을 열심히 하는 것도 중요하지만 어느 시점에 다다르면 해왔던 일을 회고하고 이야기하는 시간이 반드시 필요하다”고 강조했다.

-

- 좋아요

- 0개

-

- 슬퍼요

- 0개

-

- 화나요

- 0개

댓글 0